서브 경로

총41차시 8주 과정

김준호 외 1명 선생님

수강대상

직무영역

연구개발

생산/제조

일반/영업/마케팅

교육대상

신입

과장/선임

부장/수석

교재안내

※교재는 환급제외 대상입니다.[학습자료] 반도체 연구개발을 위한 입문 과정

0 원

수강신청

STEP1 과정유형 선택

| 수강료 |

|---|

|

410,000원 |

STEP2 개강일 선택

※교육기간은 해당 회사 인사담당자의 승인 여부에 따라 달라질 수 있습니다.

| 과정 분류 | 제목 | 모집마감일 | 교육기간 | 상태 | 강의신청 |

|---|---|---|---|---|---|

| 반도체 | 반도체 연구개발을 위한 입문 과정 | 상시모집 | 8주 상시 | 모집중 | 신청하기 |

컨텐츠 탭

훈련목표

- 반도체가 공정에 대한 전반적인 지식을 이해하고, 이를 현업에 활용할 수 있다.

- 반도체의 기본작동 동작을 이해하고, 제품별로 이해도를 높일 수 있다.

- 반도체의 생산에 이용되는 공정에 대해서 원리를 이해하고 간접 경험할 수 있다.

- 반도체 공정의 이해과정을 통해서 업무 내에서 직무 능력을 향상시킬 수 있다.

훈련대상

- 반도체 관련 기업의 업무를 진행하고 있는 사원~부장, 수석급

- 반도체 관련 기업에서 영업을 진행하고 있는 사원~부장, 수석급

- 반도체와 유사한 공정 Process를 진행하고 있는 기업의 사원~부장, 수석급

- 반도체 시장, 스마트폰 시장, IT 시장 등 IT전반에 걸친 정보가 필요한 기업의 사원 ~ 부장, 수석급

교수진소개

강사

김창호 선생님

학력

미국 Top 20 MBA 출신

경력

전) 국내 대기업 11년 근무

현) 엘캠퍼스 교강사

현) 엘캠퍼스 교강사

강사

김준호 선생님

학력

미국 TOP 10 대학원 출신

경력

현) 엘캠퍼스 교강사

전) 대기업 반도체 선행 연구 개발팀 연구원 3년

전) 연구 개발 담당 및 공정 프로세스 담당

전) 대기업 반도체 선행 연구 개발팀 연구원 3년

전) 연구 개발 담당 및 공정 프로세스 담당

수료기준

| 수료 항목 | 수료 기준 | 평가 방법 |

|---|---|---|

| 시험 | * 환급(사업주훈련) 과정 100점 만점 기준 60점 이상 * 비환급(일반) 과정 - 시험 있는 과정 : 시험 응시(점수 무관) - 시험 없는 과정 : 시험 없음(진도율로 수료) ※ 기업의 요청이 있을 경우, '수료기준'은 다를 수 있습니다. |

- 진행단계평가 선다형 문제 4문항 출제 총 100점만점, 배점 각 25점. - 최종평가 선다형 문제 10문항 출제 총 100점만점, 배점 각 10점. - 과제 서술형 문제 1문항 출제 총 100점 만점, 배점 각 100점. |

| 진도율 | * 환급(사업주훈련) 과정 진도율 100% 기준, 80% 이상 시 수료 가능 * 비환급(일반) 과정 진도율 100% 기준, 100% 이상 시 수료 가능 |

차시별 총 학습시간의 50% 이상 학습한 차시만 해당 과정의 총 진도율에 반영됩니다. |

훈련내용

| 차시 | 차시명 | 학습 목표 | 강의 시간 |

|---|---|---|---|

| 1차시 | 반도체 입문_1차시_반도체 단위소자 개발하기 기초 이론(1) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

28분 |

| 2차시 | 반도체 입문_2차시_반도체 단위소자 개발하기 기초 이론(2) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

29분 |

| 3차시 | 반도체 입문_3차시_반도체 단위소자 개발하기 기초 이론(3) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

31분 |

| 4차시 | 반도체 입문_4차시_반도체 단위소자 개발하기 (1) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

29분 |

| 5차시 | 반도체 입문_5차시_반도체 단위소자 개발하기 (2) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

32분 |

| 6차시 | 반도체 입문_6차시_반도체 단위소자 개발하기 (3) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

34분 |

| 7차시 | 반도체 입문_7차시_반도체 단위소자 개발하기 (4) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

33분 |

| 8차시 | 반도체 입문_8차시_반도체 단위소자 개발하기 (5) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

42분 |

| 9차시 | 반도체 입문_9차시_단위소자 개발_현대 MOSFET의 issue (1) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

29분 |

| 10차시 | 반도체 입문_10차시_단위소자 개발_현대 MOSFET의 issue (2) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

30분 |

| 11차시 | 반도체 입문_11차시_단위소자 개발_현대 MOSFET의 issue (3) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

27분 |

| 12차시 | 반도체 입문_12차시_반도체 단위소자 개발의 다양한 응용 (1) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

36분 |

| 13차시 | 반도체 입문_13차시_반도체 단위소자 개발의 다양한 응용 (2) | - 소자들의 특성 항목과 기준을 해석할 수 있다. - 소자들의 검증 패턴을 해석하고 적용할 수 있다. - 소자분석 장비의 사용법을 해석하고 적용할 수 있다. - 소자 특성 측정 데이터의 불량 여부를 파악할 수 있다. - 측정 데이터를 근거로 표준화된 기법에 의거, 장/단기 공정 특성산포를 예측하고 문서화할 수 있다. |

31분 |

| 14차시 | 전기 전자 회로 입문 - 1. 전기 전자 신호와 회로구성하기 | -설계하고자 하는 전체 칩의 시스템에 대한 이해를 할 수 있고 전체 회로에 대한 기능을 적절한 블록다이어그램으로 표현할 수 있다. -각 세부 블록에 대해서 주어진 설계 목표에 따라 기능 및 특성을 만족하는 회로를 설계할 수 있다. -설계 회로에 대하여 기능별로 모델링을 할 수 있으며 모델링 특성을 분석할 수 있다. -설계된 회로를 단위 소자의 매칭 특성, 온도 특성 등을 고려하여 단위회로 및 전체 블록에 대한 배치도를 설계할 수 있다. -기존에 설계된 회로를 해석하고 분석하여 설계 사양에 맞게 변경 및 적용할 수 있다. |

25분 |

| 15차시 | 전기 전자 회로 입문 - 2. 전자회로구성의 기본 개념 | -설계하고자 하는 전체 칩의 시스템에 대한 이해를 할 수 있고 전체 회로에 대한 기능을 적절한 블록다이어그램으로 표현할 수 있다. -각 세부 블록에 대해서 주어진 설계 목표에 따라 기능 및 특성을 만족하는 회로를 설계할 수 있다. -설계 회로에 대하여 기능별로 모델링을 할 수 있으며 모델링 특성을 분석할 수 있다. -설계된 회로를 단위 소자의 매칭 특성, 온도 특성 등을 고려하여 단위회로 및 전체 블록에 대한 배치도를 설계할 수 있다. -기존에 설계된 회로를 해석하고 분석하여 설계 사양에 맞게 변경 및 적용할 수 있다. |

26분 |

| 16차시 | 전기 전자 회로 입문 - 3. 전자회로구성_Kirchhoff’s Circuit Laws | -설계하고자 하는 전체 칩의 시스템에 대한 이해를 할 수 있고 전체 회로에 대한 기능을 적절한 블록다이어그램으로 표현할 수 있다. -각 세부 블록에 대해서 주어진 설계 목표에 따라 기능 및 특성을 만족하는 회로를 설계할 수 있다. -설계 회로에 대하여 기능별로 모델링을 할 수 있으며 모델링 특성을 분석할 수 있다. -설계된 회로를 단위 소자의 매칭 특성, 온도 특성 등을 고려하여 단위회로 및 전체 블록에 대한 배치도를 설계할 수 있다. -기존에 설계된 회로를 해석하고 분석하여 설계 사양에 맞게 변경 및 적용할 수 있다. |

25분 |

| 17차시 | 전기 전자 회로 입문 - 4. 전자회로구성_R,L,C의 이해 | -설계하고자 하는 전체 칩의 시스템에 대한 이해를 할 수 있고 전체 회로에 대한 기능을 적절한 블록다이어그램으로 표현할 수 있다. -각 세부 블록에 대해서 주어진 설계 목표에 따라 기능 및 특성을 만족하는 회로를 설계할 수 있다. -설계 회로에 대하여 기능별로 모델링을 할 수 있으며 모델링 특성을 분석할 수 있다. -설계된 회로를 단위 소자의 매칭 특성, 온도 특성 등을 고려하여 단위회로 및 전체 블록에 대한 배치도를 설계할 수 있다. -기존에 설계된 회로를 해석하고 분석하여 설계 사양에 맞게 변경 및 적용할 수 있다. |

30분 |

| 18차시 | 전기 전자 회로 입문 - 5. 전자회로구성_전달함수의 이해 | -설계하고자 하는 전체 칩의 시스템에 대한 이해를 할 수 있고 전체 회로에 대한 기능을 적절한 블록다이어그램으로 표현할 수 있다. -각 세부 블록에 대해서 주어진 설계 목표에 따라 기능 및 특성을 만족하는 회로를 설계할 수 있다. -설계 회로에 대하여 기능별로 모델링을 할 수 있으며 모델링 특성을 분석할 수 있다. -설계된 회로를 단위 소자의 매칭 특성, 온도 특성 등을 고려하여 단위회로 및 전체 블록에 대한 배치도를 설계할 수 있다. -기존에 설계된 회로를 해석하고 분석하여 설계 사양에 맞게 변경 및 적용할 수 있다. |

36분 |

| 19차시 | 전기 전자 회로 입문 - 6. 전자회로구성_R,L,C 회로와 필터의 이해 | -설계하고자 하는 전체 칩의 시스템에 대한 이해를 할 수 있고 전체 회로에 대한 기능을 적절한 블록다이어그램으로 표현할 수 있다. -각 세부 블록에 대해서 주어진 설계 목표에 따라 기능 및 특성을 만족하는 회로를 설계할 수 있다. -설계 회로에 대하여 기능별로 모델링을 할 수 있으며 모델링 특성을 분석할 수 있다. -설계된 회로를 단위 소자의 매칭 특성, 온도 특성 등을 고려하여 단위회로 및 전체 블록에 대한 배치도를 설계할 수 있다. -기존에 설계된 회로를 해석하고 분석하여 설계 사양에 맞게 변경 및 적용할 수 있다. |

26분 |

| 20차시 | 전기 전자 회로 입문 - 7. 전자회로구성_안정성 | -설계하고자 하는 전체 칩의 시스템에 대한 이해를 할 수 있고 전체 회로에 대한 기능을 적절한 블록다이어그램으로 표현할 수 있다. -각 세부 블록에 대해서 주어진 설계 목표에 따라 기능 및 특성을 만족하는 회로를 설계할 수 있다. -설계 회로에 대하여 기능별로 모델링을 할 수 있으며 모델링 특성을 분석할 수 있다. -설계된 회로를 단위 소자의 매칭 특성, 온도 특성 등을 고려하여 단위회로 및 전체 블록에 대한 배치도를 설계할 수 있다. -기존에 설계된 회로를 해석하고 분석하여 설계 사양에 맞게 변경 및 적용할 수 있다. |

29분 |

| 21차시 | 전기 전자 회로 입문 - 8. 전자회로 구성_MOSFET | -설계하고자 하는 전체 칩의 시스템에 대한 이해를 할 수 있고 전체 회로에 대한 기능을 적절한 블록다이어그램으로 표현할 수 있다. -각 세부 블록에 대해서 주어진 설계 목표에 따라 기능 및 특성을 만족하는 회로를 설계할 수 있다. -설계 회로에 대하여 기능별로 모델링을 할 수 있으며 모델링 특성을 분석할 수 있다. -설계된 회로를 단위 소자의 매칭 특성, 온도 특성 등을 고려하여 단위회로 및 전체 블록에 대한 배치도를 설계할 수 있다. -기존에 설계된 회로를 해석하고 분석하여 설계 사양에 맞게 변경 및 적용할 수 있다. |

26분 |

| 22차시 | 전기 전자 회로 입문 - 9. 전자회로구성_Amplifier의 기초 | -설계하고자 하는 전체 칩의 시스템에 대한 이해를 할 수 있고 전체 회로에 대한 기능을 적절한 블록다이어그램으로 표현할 수 있다. -각 세부 블록에 대해서 주어진 설계 목표에 따라 기능 및 특성을 만족하는 회로를 설계할 수 있다. -설계 회로에 대하여 기능별로 모델링을 할 수 있으며 모델링 특성을 분석할 수 있다. -설계된 회로를 단위 소자의 매칭 특성, 온도 특성 등을 고려하여 단위회로 및 전체 블록에 대한 배치도를 설계할 수 있다. -기존에 설계된 회로를 해석하고 분석하여 설계 사양에 맞게 변경 및 적용할 수 있다. |

27분 |

| 23차시 | 반도체 전공정- 1. 반도체 전공정흐름도 해석_기본 | - 웨이퍼 종류와 특성을 해석하고 설명할 수 있다. - MOSFET 제작 구조를 해석하고 설명할 수 있다. - 메탈배선의 적층 구조를 해석하고 설명할 수 있다. - 패드(Pad) 및 보호막(Passivation Layer)의 구조를 해석하고 설명할 수 있다. - 공정흐름도로부터 필요한 단위 공정을 파악할 수 있다. |

26분 |

| 24차시 | 반도체 전공정- 2. 반도체 전공정흐름도 해석_DRAM & NAND Flash 동작 원리 - 1 | - 웨이퍼 종류와 특성을 해석하고 설명할 수 있다. - MOSFET 제작 구조를 해석하고 설명할 수 있다. - 메탈배선의 적층 구조를 해석하고 설명할 수 있다. - 패드(Pad) 및 보호막(Passivation Layer)의 구조를 해석하고 설명할 수 있다. - 공정흐름도로부터 필요한 단위 공정을 파악할 수 있다. |

29분 |

| 25차시 | 반도체 전공정- 3. 반도체 전공정흐름도 해석_DRAM & NAND Flash 동작 원리 - 2 | - 웨이퍼 종류와 특성을 해석하고 설명할 수 있다. - MOSFET 제작 구조를 해석하고 설명할 수 있다. - 메탈배선의 적층 구조를 해석하고 설명할 수 있다. - 패드(Pad) 및 보호막(Passivation Layer)의 구조를 해석하고 설명할 수 있다. - 공정흐름도로부터 필요한 단위 공정을 파악할 수 있다. |

29분 |

| 26차시 | 반도체 전공정- 4. 반도체 전공정흐름도 해석_DRAM & NAND Flash 이슈 사항들 | - 웨이퍼 종류와 특성을 해석하고 설명할 수 있다. - MOSFET 제작 구조를 해석하고 설명할 수 있다. - 메탈배선의 적층 구조를 해석하고 설명할 수 있다. - 패드(Pad) 및 보호막(Passivation Layer)의 구조를 해석하고 설명할 수 있다. - 공정흐름도로부터 필요한 단위 공정을 파악할 수 있다. |

26분 |

| 27차시 | 반도체 전공정- 5. 반도체 전공정 흐름도 해석_Process - 1 | - 웨이퍼 종류와 특성을 해석하고 설명할 수 있다. - MOSFET 제작 구조를 해석하고 설명할 수 있다. - 메탈배선의 적층 구조를 해석하고 설명할 수 있다. - 패드(Pad) 및 보호막(Passivation Layer)의 구조를 해석하고 설명할 수 있다. - 공정흐름도로부터 필요한 단위 공정을 파악할 수 있다. |

27분 |

| 28차시 | 반도체 전공정- 6. 반도체 전공정 흐름도 해석_Process - 2 | - 웨이퍼 종류와 특성을 해석하고 설명할 수 있다. - MOSFET 제작 구조를 해석하고 설명할 수 있다. - 메탈배선의 적층 구조를 해석하고 설명할 수 있다. - 패드(Pad) 및 보호막(Passivation Layer)의 구조를 해석하고 설명할 수 있다. - 공정흐름도로부터 필요한 단위 공정을 파악할 수 있다. |

27분 |

| 29차시 | 반도체 전공정- 7. 반도체 전공정 흐름도 해석_Process - 3 | - 웨이퍼 종류와 특성을 해석하고 설명할 수 있다. - MOSFET 제작 구조를 해석하고 설명할 수 있다. - 메탈배선의 적층 구조를 해석하고 설명할 수 있다. - 패드(Pad) 및 보호막(Passivation Layer)의 구조를 해석하고 설명할 수 있다. - 공정흐름도로부터 필요한 단위 공정을 파악할 수 있다. |

27분 |

| 30차시 | 반도체 전공정- 8. 반도체 전공정 흐름도 해석_Process - 4 | - 웨이퍼 종류와 특성을 해석하고 설명할 수 있다. - MOSFET 제작 구조를 해석하고 설명할 수 있다. - 메탈배선의 적층 구조를 해석하고 설명할 수 있다. - 패드(Pad) 및 보호막(Passivation Layer)의 구조를 해석하고 설명할 수 있다. - 공정흐름도로부터 필요한 단위 공정을 파악할 수 있다. |

26분 |

| 31차시 | 반도체 전공정- 9. 반도체 전공정 흐름도 해석_Process - 5 | - 웨이퍼 종류와 특성을 해석하고 설명할 수 있다. - MOSFET 제작 구조를 해석하고 설명할 수 있다. - 메탈배선의 적층 구조를 해석하고 설명할 수 있다. - 패드(Pad) 및 보호막(Passivation Layer)의 구조를 해석하고 설명할 수 있다. - 공정흐름도로부터 필요한 단위 공정을 파악할 수 있다. |

28분 |

| 32차시 | 반도체 전공정- 10. 반도체 전공정 흐름도 해석_Issue & Solution | - 웨이퍼 종류와 특성을 해석하고 설명할 수 있다. - MOSFET 제작 구조를 해석하고 설명할 수 있다. - 메탈배선의 적층 구조를 해석하고 설명할 수 있다. - 패드(Pad) 및 보호막(Passivation Layer)의 구조를 해석하고 설명할 수 있다. - 공정흐름도로부터 필요한 단위 공정을 파악할 수 있다. |

26분 |

| 33차시 | 반도체 후공정- 1. 반도체 패키지 전공정(후공정) 개발하기_ 소개 | -후면연마 공정을 통해 규정되어 있는 제품별 패키지 높이를 맞추기 위해 웨이퍼의 뒷면을 기계적 또는 화학적 방법으로 연마할 수 있다. -웨이퍼 소잉(Sawing) 공정을 통해 칩(Die)을 개별적으로 분리할 수 있다. -다이 접착 공정을 통해 리드프레임이나 반도체 기판 등의 패키지 재료에 다이를 고정시킬 수 있고, 스페이서 테이프를 이용하여 추가로 반도체 칩을 적층할 수 있다. 또한 제품에 따라서 다양한 접합공정이 사용될 수 있다. -TSV(Through Silicon Via) 공정을 통해 웨이퍼에 관통 홀을 형성하여 칩과 칩 또는 웨이퍼와 웨이퍼 간의 접합으로 3차원 적층을 할 수 있다. -플라즈마 클리닝 공정을 통해 반도체 기판의 표면에 증착된 유기물을 물리, 화학적 방법으로 제거할 수 있다. |

36분 |

| 34차시 | 반도체 후공정- 2. 반도체 패키지 전공정(후공정) 개발하기_ Packaging 1 | -후면연마 공정을 통해 규정되어 있는 제품별 패키지 높이를 맞추기 위해 웨이퍼의 뒷면을 기계적 또는 화학적 방법으로 연마할 수 있다. -웨이퍼 소잉(Sawing) 공정을 통해 칩(Die)을 개별적으로 분리할 수 있다. -다이 접착 공정을 통해 리드프레임이나 반도체 기판 등의 패키지 재료에 다이를 고정시킬 수 있고, 스페이서 테이프를 이용하여 추가로 반도체 칩을 적층할 수 있다. 또한 제품에 따라서 다양한 접합공정이 사용될 수 있다. -TSV(Through Silicon Via) 공정을 통해 웨이퍼에 관통 홀을 형성하여 칩과 칩 또는 웨이퍼와 웨이퍼 간의 접합으로 3차원 적층을 할 수 있다. -플라즈마 클리닝 공정을 통해 반도체 기판의 표면에 증착된 유기물을 물리, 화학적 방법으로 제거할 수 있다. |

34분 |

| 35차시 | 반도체 후공정- 3. 반도체 패키지 전공정(후공정) 개발하기 - Packaging 2 | -후면연마 공정을 통해 규정되어 있는 제품별 패키지 높이를 맞추기 위해 웨이퍼의 뒷면을 기계적 또는 화학적 방법으로 연마할 수 있다. -웨이퍼 소잉(Sawing) 공정을 통해 칩(Die)을 개별적으로 분리할 수 있다. -다이 접착 공정을 통해 리드프레임이나 반도체 기판 등의 패키지 재료에 다이를 고정시킬 수 있고, 스페이서 테이프를 이용하여 추가로 반도체 칩을 적층할 수 있다. 또한 제품에 따라서 다양한 접합공정이 사용될 수 있다. -TSV(Through Silicon Via) 공정을 통해 웨이퍼에 관통 홀을 형성하여 칩과 칩 또는 웨이퍼와 웨이퍼 간의 접합으로 3차원 적층을 할 수 있다. -플라즈마 클리닝 공정을 통해 반도체 기판의 표면에 증착된 유기물을 물리, 화학적 방법으로 제거할 수 있다. |

30분 |

| 36차시 | 반도체 후공정- 4. 반도체 패키지 전공정(후공정) 개발하기 - 후공정 Test | -후면연마 공정을 통해 규정되어 있는 제품별 패키지 높이를 맞추기 위해 웨이퍼의 뒷면을 기계적 또는 화학적 방법으로 연마할 수 있다. -웨이퍼 소잉(Sawing) 공정을 통해 칩(Die)을 개별적으로 분리할 수 있다. -다이 접착 공정을 통해 리드프레임이나 반도체 기판 등의 패키지 재료에 다이를 고정시킬 수 있고, 스페이서 테이프를 이용하여 추가로 반도체 칩을 적층할 수 있다. 또한 제품에 따라서 다양한 접합공정이 사용될 수 있다. -TSV(Through Silicon Via) 공정을 통해 웨이퍼에 관통 홀을 형성하여 칩과 칩 또는 웨이퍼와 웨이퍼 간의 접합으로 3차원 적층을 할 수 있다. -플라즈마 클리닝 공정을 통해 반도체 기판의 표면에 증착된 유기물을 물리, 화학적 방법으로 제거할 수 있다. |

28분 |

| 37차시 | 반도체 후공정- 5. 반도체 패키지 전공정(후공정) 개발하기_Package 기술 | -후면연마 공정을 통해 규정되어 있는 제품별 패키지 높이를 맞추기 위해 웨이퍼의 뒷면을 기계적 또는 화학적 방법으로 연마할 수 있다. -웨이퍼 소잉(Sawing) 공정을 통해 칩(Die)을 개별적으로 분리할 수 있다. -다이 접착 공정을 통해 리드프레임이나 반도체 기판 등의 패키지 재료에 다이를 고정시킬 수 있고, 스페이서 테이프를 이용하여 추가로 반도체 칩을 적층할 수 있다. 또한 제품에 따라서 다양한 접합공정이 사용될 수 있다. -TSV(Through Silicon Via) 공정을 통해 웨이퍼에 관통 홀을 형성하여 칩과 칩 또는 웨이퍼와 웨이퍼 간의 접합으로 3차원 적층을 할 수 있다. -플라즈마 클리닝 공정을 통해 반도체 기판의 표면에 증착된 유기물을 물리, 화학적 방법으로 제거할 수 있다. |

31분 |

| 38차시 | 반도체 후공정- 6. 반도체 패키지 전공정(후공정) 개발하기 - TSV(Through Silicon Via) | -후면연마 공정을 통해 규정되어 있는 제품별 패키지 높이를 맞추기 위해 웨이퍼의 뒷면을 기계적 또는 화학적 방법으로 연마할 수 있다. -웨이퍼 소잉(Sawing) 공정을 통해 칩(Die)을 개별적으로 분리할 수 있다. -다이 접착 공정을 통해 리드프레임이나 반도체 기판 등의 패키지 재료에 다이를 고정시킬 수 있고, 스페이서 테이프를 이용하여 추가로 반도체 칩을 적층할 수 있다. 또한 제품에 따라서 다양한 접합공정이 사용될 수 있다. -TSV(Through Silicon Via) 공정을 통해 웨이퍼에 관통 홀을 형성하여 칩과 칩 또는 웨이퍼와 웨이퍼 간의 접합으로 3차원 적층을 할 수 있다. -플라즈마 클리닝 공정을 통해 반도체 기판의 표면에 증착된 유기물을 물리, 화학적 방법으로 제거할 수 있다. |

26분 |

| 39차시 | 반도체 후공정 - 7. 통계적 공정관리 | - 공정상에 활용 할 수 있는 통계의 종류를 알 수 있다. - 통계적 공정 관리를 통해 품질 문제를 예방 할 수 있으며 이상점을 관리 할 수 있다. |

38분 |

| 40차시 | 반도체 후공정 - 8. 공정 문제 해결 기법 | - 공정상에 발생되는 품질 문제에 대비하여 문제 해결 기법을 알고 대응하자. | 26분 |

| 41차시 | 반도체 후공정 - 9. 반도체 패키지 전공정(후공정) 개발하기_공정관리 | -후면연마 공정을 통해 규정되어 있는 제품별 패키지 높이를 맞추기 위해 웨이퍼의 뒷면을 기계적 또는 화학적 방법으로 연마할 수 있다. -웨이퍼 소잉(Sawing) 공정을 통해 칩(Die)을 개별적으로 분리할 수 있다. -다이 접착 공정을 통해 리드프레임이나 반도체 기판 등의 패키지 재료에 다이를 고정시킬 수 있고, 스페이서 테이프를 이용하여 추가로 반도체 칩을 적층할 수 있다. 또한 제품에 따라서 다양한 접합공정이 사용될 수 있다. -TSV(Through Silicon Via) 공정을 통해 웨이퍼에 관통 홀을 형성하여 칩과 칩 또는 웨이퍼와 웨이퍼 간의 접합으로 3차원 적층을 할 수 있다. -플라즈마 클리닝 공정을 통해 반도체 기판의 표면에 증착된 유기물을 물리, 화학적 방법으로 제거할 수 있다. |

26분 |

수강후기

더보기

| 번호 | 과정 분류 | 제목 | 등록일 | 조회수 |

|---|---|---|---|---|

| 10 | 반도체 | 좋은 강의 감사합니다. | 2024-03-28 | 35 |

| 9 | 반도체 | 공정에 대해 심도있게 알 수 있었습니다. | 2024-03-26 | 47 |

| 8 | 반도체 | 잘 들었습니다 | 2024-03-05 | 63 |

| 7 | 반도체 | 반도체 공정이론 후기 | 2024-02-29 | 66 |

| 6 | 반도체 | 도움이됐습니다 | 2024-02-20 | 84 |

| 5 | 반도체 | 굳 | 2024-02-14 | 77 |

| 4 | 반도체 | 반도체 환경 설비 직무향상에 도움이됩니다 | 2024-01-26 | 105 |

| 3 | 반도체 | 막연했던 그림이 구체적으로.... | 2023-12-03 | 167 |

| 2 | 반도체 | 교육 | 2023-11-06 | 151 |

| 1 | 반도체 | 유익한 정보를 많이 배웠습니다. | 2023-09-21 | 234 |

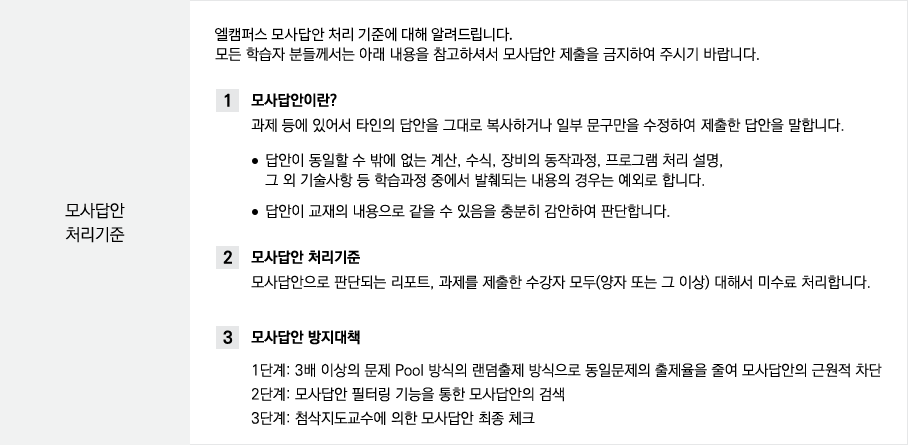

유의사항